# XTS315-10LY

25 Gb/s 10 km SFP28 Transceiver

# Applications

- High-speed storage area networks

- Computer cluster cross-connect

- Custom high-speed data pipes

# Features

- 25 Gb/s serial optical interface

- 1310 nm DFB transmitter, PIN photodetector

- 2-wire interface for management specifications compliant with SFF 8472 digital diagnostic monitoring interface for optical transceivers

- Operating case temperature: 0 °C to 70 °C

- Advanced firmware allow customer system encryption information to be stored in transceiver

- Cost effective SFP28 solution, enables higher port densities and greater bandwidth

- RoHS compliant

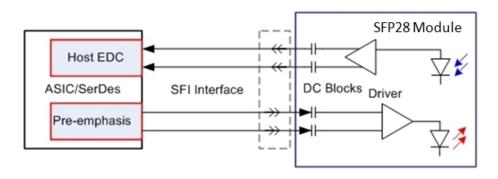

Figure 1: Application in the System

#### **Description:**

This 1310 nm DFB 25 Gigabit SFP28 transceiver is designed to transmit and receive optical data over single mode optical fiber for link length 10km.

The SFP28 LR module electrical interface is compliant to SFI electrical specifications. The transmitter input and receiver output impedance is 100 Ohms differential. Data lines are internally AC coupled. The module provides differential termination and reduce differential to common mode conversion for quality signal termination and low EMI. SFI typically operates over 200 mm of improved FR4 material or up to about 150 mm of standard FR4 with one connector.

The transmitter converts 25 Gbit/s serial PECL or CML electrical data into serial optical data compliant with the 25GBASE-LR standard. An open collector compatible Transmit Disable (Tx\_Dis) is provided. Logic "1" or no connection on this pin will disable the laser from transmitting. Logic "0" on this pin provides normal operation. The transmitter has an internal automatic power control loop (APC) to ensure constant optical power output across supply voltage and temperature variations. An open collector compatible Transmit Fault (Tx\_Fault) is provided. TX\_Fault is module output contact that when high, indicates that the module transmitter has detected a fault condition related to laser operation or safety. The TX\_Fault output contact is an open drain/collector and shall be pulled up to the Vcc\_Host in the host with a resistor in the range 4.7-10 k $\Omega$ . TX\_Disable is a module input contact. When TX\_Disable is asserted high or left open, the SFP28 module transmitter output shall be turned off. This contact shall be pulled up to VccT with a 4.7 k $\Omega$  to 10 k $\Omega$  resistor

The receiver converts 25Gbit/s serial optical data into serial PECL/CML electrical data. An open collector compatible Loss of Signal is provided. Rx\_LOS when high indicates an optical signal level below that specified in the relevant standard. The Rx\_LOS contact is an open drain/collector output and shall be pulled up to Vcc\_Host in the host with a resistor in the range 4.7-10 k $\Omega$ , or with an active termination. Power supply filtering is recommended for both the transmitter and receiver. The Rx\_LOS signal is intended as a preliminary indication to the system in which the SFP28 is installed that the received signal strength is below the specified range. Such an indication typically points to non-installed cables, broken cables, or a disabled, failing or a powered off transmitter at the far end of the cable.

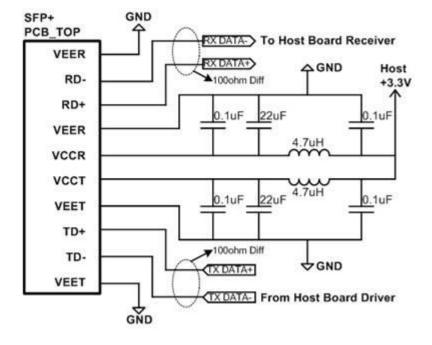

# 2. Proposed Application Schematics

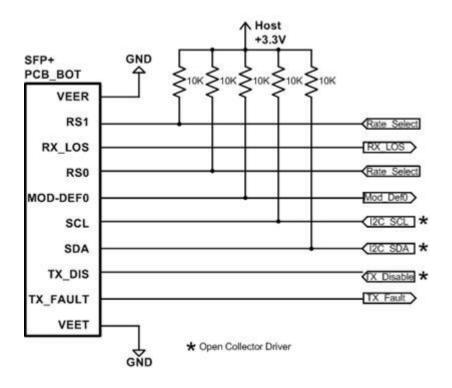

### 3. Pin Definition

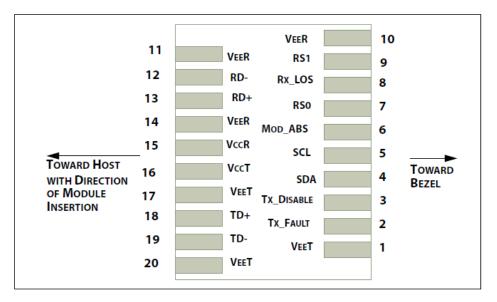

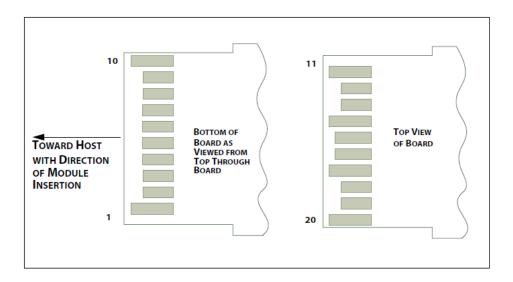

The SFP28 modules are hot-pluggable. Hot pluggable refers to plugging in or unplugging a module while the host board is powered. The SFP28 host connector is a 0.8 mm pitch 20 position right angle improved connector specified by SFF-8083, or stacked connector with equivalent with equivalent electrical performance. Host PCB contact assignment is shown in Figure 3 and contact definitions are given in the PIN description table. SFP28 module contacts mates with the host in the order of ground, power, followed by signal as illustrated by Figure 4 and the contact sequence order listed in the PIN description table.

Figure 3: Module Interface to Host

Figure 4: Module Contact Assignment

| PIN | Logic     | Symbol   | Name / Description                                      | Note |

|-----|-----------|----------|---------------------------------------------------------|------|

| 1   |           | VeeT     | Module Transmitter Ground                               | 1    |

| 2   | LVTTL-O   | TX_Fault | Module Transmitter Fault                                |      |

| 3   | LVTTL-I   | TX_Dis   | Transmitter Disable; Turns off transmitter laser output |      |

| 4   | LVTTL-I/O | SDA      | 2-Wire Serial Interface Data Line                       | 2    |

| 5   | LVTTL-I   | SCL      | 2-Wire Serial Interface Clock                           | 2    |

| 6   |           | MOD_DEF0 | Module Definition, Grounded in the module               |      |

| 7   | LVTTL-I   | RSO      | Receiver Rate Select                                    |      |

| 8   | LVTTL-O   | RX_LOS   | Receiver Loss of Signal Indication Active LOW           |      |

| 9   | LVTTL-I   | RS1      | Transmitter Rate Select (not used)                      |      |

| 10  |           | VeeR     | Module Receiver Ground                                  | 1    |

| 11  |           | VeeR     | Module Receiver Ground                                  | 1    |

| 12  | CML-O     | RD-      | Receiver Inverted Data Output                           |      |

| 13  | CML-O     | RD+      | Receiver Data Output                                    |      |

| 14  |           | VeeR     | Module Receiver Ground                                  | 1    |

| 15  |           | VccR     | Module Receiver 3.3 V Supply                            |      |

| 16  |           | VccT     | Module Receiver 3.3 V Supply                            |      |

| 17  |           | VeeT     | Module Transmitter Ground                               | 1    |

| 18  | CML-I     | TD+      | Transmitter Non-Inverted Data Input                     |      |

| 19  | CML-I     | TD-      | Transmitter Inverted Data Input                         |      |

| 20  |           | VeeT     | Module Transmitter Ground                               | 1    |

#### **PIN description**

Note:

1. Module ground pins GND are isolated from the module case.

2. Shall be pulled up with 4.7 K-10 K ohms to a voltage between 3.15V and 3.45V on the host board.

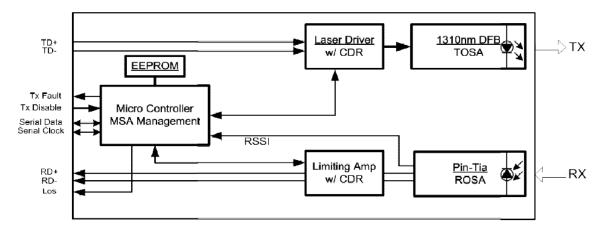

#### 4. Transceiver Block Diagram

#### 5. Absolute Maximum Ratings

These values represent the damage threshold of the module. Stress in excess of any of the individual Absolute Maximum Ratings can cause immediate catastrophic damage to the module even if all other parameters are within Recommended Operating Conditions.

| Parameters                 | Symbol | Min. | Max. | Unit |

|----------------------------|--------|------|------|------|

| Power Supply Voltage       | VCC    | 0    | 3.6  | V    |

| Storage Temperature        | Тс     | -40  | 85   | °C   |

| Operating Case Temperature | Тс     | 0    | 70   | °C   |

| Relative Humidity          | RH     | 5    | 95   | %    |

| Damage Threshold           | Pmax   | 5    |      | dBm  |

## 6. Recommended Operating Environment

Recommended Operating Environment specifies parameters for which the electrical and optical characteristics hold unless otherwise noted.

| Parameters                    | Symbol | Min.  | Typical | Max   | Unit |

|-------------------------------|--------|-------|---------|-------|------|

| Power Supply Voltage          | VCC    | 3.135 | 3.3     | 3.465 | V    |

| Power Supply Current          | lcc    |       |         | 450   | mA   |

| Operating Case<br>Temperature | тс     | 0     | 25      | 70    | °C   |

## 7. Optical Characteristics

The following optical characteristics are defined over the Recommended Operating Environment unless otherwise specified.

| Parameter                                     | Symbol | Min. | Typical | Max   | Unit  | Notes              |  |  |

|-----------------------------------------------|--------|------|---------|-------|-------|--------------------|--|--|

| Transmitter                                   |        |      |         |       |       |                    |  |  |

| Center Wavelength                             | λt     | 1290 |         | 1330  | nm    |                    |  |  |

| Side Mode Suppression Ratio                   | SMSR   | 30   |         |       | dB    |                    |  |  |

| Average Optical Power                         | Pavg   | -8.4 | -       | 3     | dBm   | 1                  |  |  |

| Laser Off Power                               | Poff   | -    | -       | -30   | dBm   |                    |  |  |

| Extinction Ratio                              | ER     | 3.5  | -       | -     | dB    |                    |  |  |

| Transmitter Dispersion Penalty                | TDP    | -    | -       | -     | dB    | TBD                |  |  |

| Relative Intensity Noise                      | Rin    | -    | -       | -     | dB/Hz | 12dB<br>reflection |  |  |

| Optical Return Loss Tolerance                 |        | -    | -       | -     | dB    | TBD                |  |  |

| Receiver                                      |        |      |         |       |       |                    |  |  |

| Center Wavelength                             | λr     | 1260 |         | 1360  | nm    |                    |  |  |

| Receiver Sensitivity in average power         | Psens  | -    | -       | -10.4 | dBm   | 1                  |  |  |

| Receiver Sensitivity in OMA                   | Psens  | -    | -       | -8.6  | dBm   | 2                  |  |  |

| Stressed Sensitivity (OMA)                    |        | -    | -       | -6.8  | dBm   | 2                  |  |  |

| Stressed eye jitter                           |        | -    |         |       | Ulp-p | TBD                |  |  |

| Receive electrical 3dB upper cutoff frequency |        |      |         |       | GHz   | TBD                |  |  |

| LOS Assert                                    | LOSA   | -    | -       | -     | dBm   | TBD                |  |  |

| LOS Deassert                                  | LOSD   | -    | -       | -     | dBm   | TBD                |  |  |

| LOS Hysteresis                                | LOSH   | -    | -       | -     | dB    | TBD                |  |  |

| Overload                                      | Pin    | -    | -       | 3.5   | dBm   | 1                  |  |  |

| Receiver power damage                         |        |      |         | 5     | dBm   |                    |  |  |

| Receiver Reflectance                          |        | -    | -       | -12   | dB    |                    |  |  |

Notes:

- 1. Average optical power shall be measured using the methods specified in TIA/EIA-455-95.

- 2. Receiver sensitivity is informative. Stressed receiver sensitivity shall be measured with conformance test signal for BER =1 x  $10^{-12}$ .

- 3. Vertical eye closure penalty and stressed eye jitter are the test conditions for measuring stressed receiver sensitivity. They are not the required characteristic of the receiver.

#### 8. Digital Diagnostic Functions

The following digital diagnostic characteristics are defined over the Recommended Operating Environment unless otherwise specified. It is compliant to SFF8472 Rev10.2 with internal calibration mode. For external calibration mode please contact our sales staff.

| Parameter                                | Symbol    | Min. | Max | Unit | Notes                   |

|------------------------------------------|-----------|------|-----|------|-------------------------|

| Temperature monitor<br>absolute error    | DMI_Temp  | -3   | 3   | degC | Over operating temp     |

| Laser power monitor<br>absolute error    | DMI_TX    | -3   | 3   | dB   |                         |

| RX power monitor absolute error          | DMI_RX    | -3   | 3   | dB   | -1 dBm to -15 dBm range |

| Supply voltage monitor<br>absolute error | DMI_VCC   | -0.1 | 0.1 | V    | Full operating range    |

| Bias current monitor                     | DMI_lbias | -10% | 10% | mA   |                         |

# 9. Electrical Characteristics

The following electrical characteristics are defined over the Recommended Operating Environment unless otherwise specified.

| Parameter                                | Symbol | Min.     | Typical | Max  | Unit | Notes        |

|------------------------------------------|--------|----------|---------|------|------|--------------|

| Data Rate                                |        | -        | 25.78   | -    | Gbps |              |

| Power Consumption                        |        | -        | 1200    | 1500 | mW   |              |

|                                          | 1      | Transmit | ter     |      |      |              |

| Single Ended Output Voltage<br>Tolerance |        | -0.3     | -       | 4    | V    |              |

| C common mode voltage<br>tolerance       |        | 15       | -       | -    | mV   |              |

| Tx Input Diff Voltage                    | VI     | 180      |         | 700  | mV   |              |

| Tx Fault                                 | VoL    | -0.3     |         | 0.4  | V    | At 0.7 mA    |

| Data Dependent Input Jitter              | DDJ    |          |         | 0.1  | UI   |              |

| Data Input Total Jitter                  | ΤJ     | -        | -       | -    | UI   | TBD          |

|                                          | -      | Receive  | er      |      |      |              |

| Single Ended Output Voltage<br>Tolerance |        | -0.3     | -       | 4    | V    |              |

| Rx Output Diff Voltage                   | Vo     | 300      |         | 900  | mV   |              |

| Rx Output Rise and Fall Time             | Tr/Tf  | 9.5      |         |      | ps   | 20 % to 80 % |

| Total Jitter                             | TJ     | -        | -       | -    | UI   | TBD          |

| Deterministic Jitter                     | DJ     | -        | -       | -    | UI   | TBD          |

# 10. Control and Status I/O Timing Characteristics

Timing characteristics of control and status I/O are included in the Table 8.

| Parameter                                                                                     | Symbol                | Min. | Max. | Unit | Conditions                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------|-----------------------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tx_Disable assert time                                                                        | t_off                 |      | 100  | μs   | Rising edge of Tx_Disable to fall of output signal below 10% of nominal                                                                                                                                                                                                                                                                                           |

| Tx_Disable negate time                                                                        | t_on                  |      | 2    | ms   | Falling edge of Tx_Disable to rise of output signal<br>above 90% of nominal. This only applies in normal<br>operation, not during start up or fault recovery.                                                                                                                                                                                                     |

| Time to initialize 2-wire interface                                                           | t_2w_start_up         |      | 300  | ms   | From power on or hot plug after the supply meet-<br>ing <u>Table 8</u> .                                                                                                                                                                                                                                                                                          |

| Time to initialize                                                                            | t_start_up            |      | 300  | ms   | From power supplies meeting <u>Table 8</u> or hot plug<br>or Tx disable negated during power up, or<br>Tx_Fault recovery, until non-cooled power level I<br>part (or non-cooled power level II part already<br>enabled at power level II for Tx_Fault recovery) is<br>fully operational.                                                                          |

| Time to initialize cooled module<br>and time to power up a cooled<br>module to Power Level II | t_start_up_cooled     |      | 90   | S    | From power supplies meeting <u>Table 8</u> or hot plug,<br>or Tx disable negated during power up or Tx_Fault<br>recovery, until cooled power level I part (or cooled<br>power level II part during fault recovery) is fully<br>operational. Also, from stop bit low-to-high SDA<br>transition enabling Power Level II until cooled<br>module is fully operational |

| Time to Power Up to Level II                                                                  | t_power_level2        |      | 300  | ms   | From stop bit low-to-high SDA transition enabling<br>power level II until non-cooled module is fully<br>operational                                                                                                                                                                                                                                               |

| Time to Power Down from Level II                                                              | t_power_down          |      | 300  | ms   | From stop bit low-to-high SDA transition dis-<br>abling power level II until module is within power<br>level I requirements                                                                                                                                                                                                                                       |

| Tx_Fault assert                                                                               | Tx_Fault_on           |      | 1    | ms   | From occurrence of fault to assertion of Tx_Fault                                                                                                                                                                                                                                                                                                                 |

| Tx_Fault assert for cooled module                                                             | Tx_Fault_on_cooled    |      | 50   | ms   | From occurrence of fault to assertion of Tx_Fault                                                                                                                                                                                                                                                                                                                 |

| Tx_Fault Reset                                                                                | t_reset               | 10   |      | μs   | Time Tx_Disable must be held high to reset Tx_Fault                                                                                                                                                                                                                                                                                                               |

| RS0, RS1 rate select timing for FC                                                            | t_RS0_FC,<br>t_RS1_FC |      | 500  | μs   | From assertion till stable output                                                                                                                                                                                                                                                                                                                                 |

| RS0, RS1 rate select timing non FC                                                            | t_RS0, t_RS1          |      | 24   | ms   | From assertion till stable output                                                                                                                                                                                                                                                                                                                                 |

| Rx_LOS assert delay                                                                           | t_los_on              |      | 100  | μs   | From occurrence of loss of signal to assertion of Rx_LOS                                                                                                                                                                                                                                                                                                          |

| Rx_LOS negate delay                                                                           | t_los_off             |      | 100  | μs   | From occurrence of presence of signal to negation of Rx_LOS                                                                                                                                                                                                                                                                                                       |

Table 8

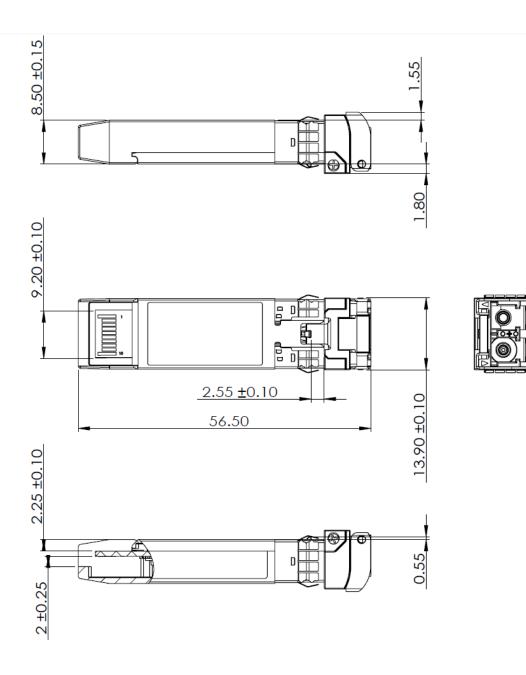

# **11.** Mechanical Dimensions

Comply with SFF-8432 rev. 5.0, the improved Pluggable form factor specification.

#### 12. ESD

This transceiver is specified as ESD threshold 1kV for SFI pins and 2kv for all others electrical input pins, tested per MIL-STD-883, Method 3015.4 /JESD22-A114-A (HBM). However, normal ESD precautions are still required during the handling of this module. This transceiver is shipped in ESD protective packaging. It should be removed from the packaging and handled only in an ESD protected environment.

## 13. Laser Safety

This is a Class 1 Laser Product according to IEC 60825-1:2007. This product complies with 21 CFR 1040.10 and 1040.11 except for deviations pursuant to Laser Notice No. 50, dated (June 24, 2007).

#### Ordering information<sup>1</sup>

| PN          | Description                                             |

|-------------|---------------------------------------------------------|

| XTS315-10LY | SFP28 Transceiver, SM, 1310 nm, 25 Gb/s, 10 km, LC, DDM |

Notes:

<sup>1</sup> For accurate order specification please contact Xenopt reseller before placing an order. The content of this document is subject to change without notice. Xenopt does not guarantee errorless or outdated information. Please specify any compatibility requirements at time of ordering.

Performance figures, data and any illustrative material provided in this data sheet are typical and must be specifically confirmed in writing by XenOpt before they become applicable to any particular order or contract. In accordance with the XenOpt policy of continuous improvement specifications may change without notice.

The publication of information in this data sheet does not imply freedom from patent or other protective rights of XenOpt or others. Further details are available from any XenOpt sales representative.

To find out more, please contact: